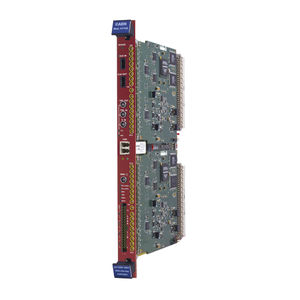

最大62.5MS/sデジタイザ 64チャネル12ビットPCI Express

お気に入りに追加する

商品比較に追加する

特徴

- 速度

- 最大62.5MS/s

- チャンネル数

- 64チャネル

- 特性

- 12ビット, PCI Express, VME

詳細

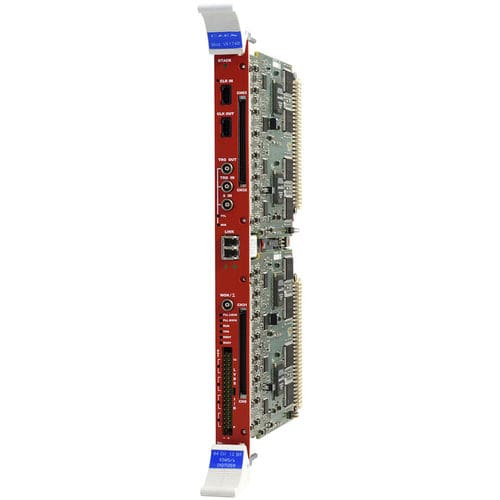

V1740は1ユニット幅のVME 6Uモジュールで、64チャネル12ビット62.5MS/s(外部クロック使用時65MS/s)フラッシュADC波形デジタイザを内蔵し、2つのERNI SMCコネクタに2Vppシングルエンド入力ダイナミクスを備えています。10Vpp(シングルエンド)入力フルスケールレンジのバージョンもあります(V1740A/V1740C)。

プログラム可能な16ビットDAC(各8チャンネル・グループに1つずつ)によるDCオフセット調整(範囲±1 V / 5 V)により、ダイナミック分解能を失うことなく、バイポーラ(Vin = ±1 V / 5 V)からフル・プラス(Vin = 0 ÷ +2 V / 10 V)またはマイナス(Vin = 0 ÷ -2 V / 10 V)のアナログ入力スイングを正しくサンプリングできます。

このモジュールは、フロント・パネルのクロック入出力と、内部/外部基準からのクロック合成用PLLを備えています。データ・ストリームはサーキュラー・メモリ・バッファに連続的に書き込まれます。トリガーが発生すると、FPGAはポストトリガー用にさらにN個のサンプルを書き込み、VMEbusまたは光リンクで読み込めるバッファをフリーズします。このバッファはVMEbusまたは光リンクで読み出すことができます。

各チャンネルは1÷1024のプログラマブル・サイズのバッファに分割可能なSRAMマルチイベント・バッファを持っています。フリーズしたバッファの読み出し(VMEbusまたはオプティカル・リンクによる)は、アクティブ・バッファ(ADCデータ・ストレージ)の書き込み動作から独立しています。チャンネル・デジタル・メモリは、オプションで2つのサイズが選択可能です:192kS/ch(V1740/V1740C)と1.5MS/ch(V1740A/V1740B)。

V1740はマルチボード同期をサポートしており、すべてのADCを共通のクロック・ソースに同期させ、トリガのタイム・スタンプを確実に揃えることができます。一度同期されると、すべてのデータは複数のV1740ボード間でアライメントされ、コヒーレントとなります。

---

カタログ

この商品のカタログはありません。

CAEN Spaの全カタログを見る*価格には税、配送費、関税また設置・作動のオプションに関する全ての追加費用は含まれておりません。表示価格は、国、原材料のレート、為替相場により変動することがあります。