- ロボット・自動装置・産業用IT

- 産業用ソフトウェア

- デザインソフトウェア

- SIEMENS EDA/シーメンス

可視化ソフトウェア Xpedition Substrate Integratorデザイン管理プロトタイピング

お気に入りに追加する

商品比較に追加する

特徴

- 機能

- 管理, 可視化, デザイン, 計画用, 最適化, 検査, 接続, プロトタイピング

- 応用

- プロセス

- タイプ

- 3D

詳細

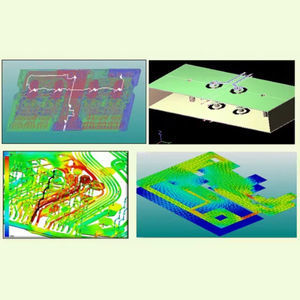

ヘテロジニアスおよびホモジニアス2.5/3D ICパッケージ接続プランニング、アセンブリプロトタイピング、システム技術の共同最適化。

2.5/3D ICパッケージのプランニングとプロトタイピング

早期のプロトタイピングと調査により、エンジニアは詳細な物理的実装に先立ち、全体的なPPA、デバイス・サイズ、配線性、コスト目標を達成するために、さまざまなASIC/チップレット、インターポーザー、パッケージ、PCB統合シナリオを評価できます。

Substrate Integratorの主な特長

完全または部分的な回路図のインポート

SiPモジュールのようなデバイス数の多い設計や、過去の設計の再利用/リターゲティングに便利です。

システムレベルのパッケージ接続管理

マルチダイ、マルチコンポーネント、マルチ基板ICパッケージ設計のシステムコネクティビティ管理、可視化、システムレベルの論理検証を行います。

ダイ、チップレット、サブストレートの集約

Xpedition Substrate Integratorは、異なるプロセスノードやサプライヤのダイ、チップレット、インターポーザを統合します。LEF/DEF、GDS、AIF、CSV/TXTなど、複数のフォーマットに対応しています。階層化されたバーチャル・ダイ・モデルは、設計/最適化中のオブジェクトの双方向のECO変更をサポートします。

シリコン-パッケージ-PCBクロス基板協調最適化

クロスサブストレート・プランニングと協調最適化により、実装時の予測可能性が大幅に向上します。 基板横断的な可視性を持つシステム視点は、通常個々の基板ベースで行われる決定への即時フィードバックを通じて、コミュニケーションと調整を改善します。

---

カタログ

関連サーチ

- オートメーションソフトウェア・ソリューション

- 管理ソフトウェア・ソリューション

- 分析ソフトウェア・ソリューション

- プロセスソフトウェア・ソリューション

- Windowsソフトウェア・ソリューション

- CAD(コンピューター支援設計)システムソフトウェア

- 制御ソフトウェア・ソリューション

- リアルタイムソフトウェア・ソリューション

- オンラインソフトウェア

- デザインソフトウェア・ソリューション

- 3Dソフトウェア・ソリューション

- 測定用ソフトウェア

- インターフェイスソフトウェア

- 工業用ソフトウェア

- 品質ソフトウェア

- シミュレーション用ソフトウェア

- 可視化ソフトウェア・ソリューション

- 自動ソフトウェア

- 開発用ソフトウェア

- ネットワークソフトウェア・ソリューション