- ロボット・自動装置・産業用IT

- 産業用ソフトウェア

- 制御ソフトウェア

- SIEMENS EDA/シーメンス

制御ソフトウェア Package Signoffデザインインターフェイス検査

お気に入りに追加する

商品比較に追加する

特徴

- 機能

- インターフェイス, 制御, デザイン, 検査

- 応用

- プロセス, 排水用

- タイプ

- 自動, 2D-3D

詳細

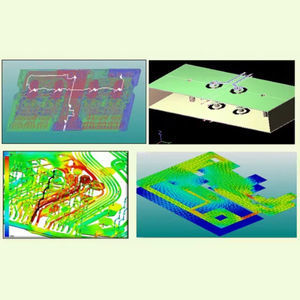

アセンブリ内のダイ配置ごとにレイヤごとのジオメトリを特定することで、複数のダイと基板アセンブリの設計検証を行います。DRCとLVSは、複数のプロセスのダイをサポートするダイ間のインターフェイス形状に対して実行されます。

ファウンドリ/OSAT主導の基板検証

性能とTime-to-Marketが潜在的な収益性を左右する場合、Calibre nmDRCをフィジカル検証に使用することで成功が可能になります。微細化する形状や複雑な製造手法の要求に応えるために進化し続けるキャリバーのルールデッキは、必要となるずっと前から実証されています。

左シフト インデザイン ファブリケーション DRC

次世代パッケージング・ソリューションでは、設計者が効率的で反復可能な自動化されたフローでこれらすべてのプロセスを管理できる単一の環境内で、物理的、電気的、熱的、および製造性能に関する実証済みの自動サインオフが必要とされます。検証のためにCalibreとHyperLynxを活用することで、設計者は最終的なサインオフの前に問題を特定し、解決することができます。

ファウンドリ/OSATルール駆動型基板メタル検証

方程式ベースのDRCテクノロジー(eqDRC)は、複雑な設計やプロセスの相互作用の多くに、ユーザーによる拡張性と高速な実行時間をもたらします。eqDRCは、性能や製造性に直接的な影響を与える2D/3D相互作用だけでなく、複雑で多変数、非マンハッタン形状の精密かつ正確な特性評価を可能にします。

2.5/3D積層ダイ・アセンブリのサインオフ検証

スタック・ダイ・アセンブリの完全な設計検証を提供します。

---

カタログ

この商品のカタログはありません。

SIEMENS EDAの全カタログを見る関連サーチ

- オートメーションソフトウェア・ソリューション

- 管理ソフトウェア・ソリューション

- 分析ソフトウェア・ソリューション

- プロセスソフトウェア・ソリューション

- Windowsソフトウェア・ソリューション

- CAD(コンピューター支援設計)システムソフトウェア

- 制御ソフトウェア・ソリューション

- リアルタイムソフトウェア・ソリューション

- オンラインソフトウェア

- デザインソフトウェア・ソリューション

- 3Dソフトウェア・ソリューション

- 測定用ソフトウェア

- インターフェイスソフトウェア

- 工業用ソフトウェア

- 品質ソフトウェア

- シミュレーション用ソフトウェア

- 可視化ソフトウェア・ソリューション

- 自動ソフトウェア

- 開発用ソフトウェア

- ネットワークソフトウェア・ソリューション