- ロボット・自動装置・産業用IT

- 産業用ソフトウェア

- デザインソフトウェア

- SIEMENS EDA/シーメンス

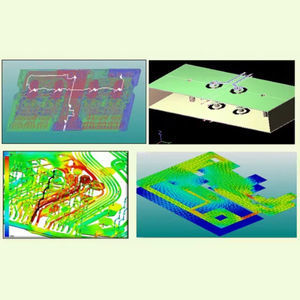

デザインソフトウェア 3D IC design solutions分析プロトタイピング開発用

お気に入りに追加する

商品比較に追加する

特徴

- 機能

- 分析, 開発用, デザイン, 計画用, 最適化, 検査, プロトタイピング, 相互シミュレーション

- 応用

- プロセス, 排水用

- タイプ

- 3D, 自動

詳細

FCBGA、FOWLP、2.5/3D ICなど、さまざまな集積技術に対応した、プランニング、プロトタイピングからサインオフまでをカバーする統合ICパッケージング・ソリューションです。当社の3D ICパッケージング・ソリューションは、モノリシック・スケーリングの限界を克服するのに役立ちます。

3D IC技術とは?

半導体業界は過去40年間、ASIC技術を飛躍的に進歩させ、性能向上に導いてきました。しかし、ムーアの法則が限界に近づくにつれ、デバイスの微細化は難しくなっています。デバイスの縮小には時間がかかり、コストがかかり、技術、設計、解析、製造に課題があります。こうして3D ICが登場した。

シーメンスの3D IC設計フローツールの主な利点

3D ICの統合とパッケージングにシステム協調最適化で取り組み、要件とリソースのバランスを取り、PPAとコストへの下流工程の影響を可視化します。

3D ICのデジタルトランスフォーメーション

共同設計、共同シミュレーション、自動化されたシステム解析とチェックにより、3Dチップ設計のデジタル・トランスフォーメーションを実現します。手作業によるインターフェースやデータ交換を、自動化された手法と定義されたワークフローに置き換えます。

3D ICの検証と妥当性確認

予測から最終サインオフまで、性能検証と設計検証のための包括的な3D ICパッケージング・カバレッジ。自動化されたレビューにより、チップ設計プロセスの早い段階で明白な問題を特定し、繰り返しを排除します。

3D IC設計リソースの有効活用

コンカレント開発のためのチームベース設計をサポートし、IPの再利用と管理ブロックを可能にします。1つのチップレット・レイアウト・ツールを有機基板とシリコン基板に活用することで、より優れたアドバンスド・パッケージング設計を実現します。

---

カタログ

この商品のカタログはありません。

SIEMENS EDAの全カタログを見る関連サーチ

- オートメーションソフトウェア・ソリューション

- 管理ソフトウェア・ソリューション

- 分析ソフトウェア・ソリューション

- プロセスソフトウェア・ソリューション

- Windowsソフトウェア・ソリューション

- CAD(コンピューター支援設計)システムソフトウェア

- 制御ソフトウェア・ソリューション

- リアルタイムソフトウェア・ソリューション

- オンラインソフトウェア

- デザインソフトウェア・ソリューション

- 3Dソフトウェア・ソリューション

- インターフェイスソフトウェア

- 測定用ソフトウェア

- 工業用ソフトウェア

- 品質ソフトウェア

- シミュレーション用ソフトウェア

- 可視化ソフトウェア・ソリューション

- 自動ソフトウェア

- 開発用ソフトウェア

- ネットワークソフトウェア・ソリューション