- ロボット・自動装置・産業用IT

- 産業用ソフトウェア

- プログラミングソフトウェア

- The MathWorks

プログラミングソフトウェア HDL Coder™FPGA

お気に入りに追加する

商品比較に追加する

特徴

- 機能

- プログラミング

- 応用

- FPGA

詳細

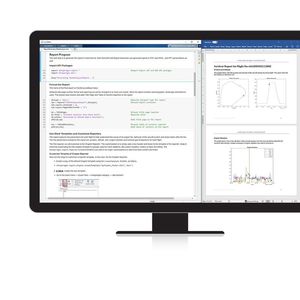

HDL Coder は、MATLAB® 関数、Simulink® モデル、および Stateflow® チャートから、移植可能で合成可能な Verilog® コードおよび VHDL® コードを生成します。生成された HDL コードは、FPGA プログラミングと、ASIC プロトタイピングおよび設計に使用できます。

HDL Coder には、Xilinx®、Microsemi®、および Intel® FPGA のプログラミングを自動化するワークフロー アドバイザーがあります。HDL アーキテクチャや実装の設定 (49:42)、クリティカルパスの強調表示、ハードウェアリソースの使用状況の推定を行うことができます。HDL Coder は、Simulink モデルと、生成された Verilog/VHDL コードの間のトレーサビリティを実現します。これにより、DO-254 などの標準規格に準拠する高信頼性アプリケーションのコードを検証できます。

ビデオ

カタログ

関連サーチ

- オートメーションソフトウェア・ソリューション

- 管理ソフトウェア・ソリューション

- 分析ソフトウェア・ソリューション

- プロセスソフトウェア・ソリューション

- CAD(コンピューター支援設計)システムソフトウェア

- Windowsソフトウェア・ソリューション

- 制御ソフトウェア・ソリューション

- オンラインソフトウェア

- リアルタイムソフトウェア・ソリューション

- デザインソフトウェア・ソリューション

- 3Dソフトウェア・ソリューション

- 測定用ソフトウェア

- シミュレーション用ソフトウェア

- 可視化ソフトウェア・ソリューション

- プログラミングソフトウェア

- 自動ソフトウェア

- ネットワークソフトウェア・ソリューション

- 装置ソフトウェア

- エンジニアリングソフトウェア

- 試験用ソフトウェア