- ロボット・自動装置・産業用IT >

- 産業用PC >

- 32チャンネルデジタイザ

32チャンネルデジタイザ

{{product.productLabel}} {{product.model}}

{{#if product.featureValues}}{{product.productPrice.formattedPrice}} {{#if product.productPrice.priceType === "PRICE_RANGE" }} - {{product.productPrice.formattedPriceMax}} {{/if}}

{{#each product.specData:i}}

{{name}}: {{value}}

{{#i!=(product.specData.length-1)}}

{{/end}}

{{/each}}

{{{product.idpText}}}

{{product.productLabel}} {{product.model}}

{{#if product.featureValues}}{{product.productPrice.formattedPrice}} {{#if product.productPrice.priceType === "PRICE_RANGE" }} - {{product.productPrice.formattedPriceMax}} {{/if}}

{{#each product.specData:i}}

{{name}}: {{value}}

{{#i!=(product.specData.length-1)}}

{{/end}}

{{/each}}

{{{product.idpText}}}

... デジタイザ - LXI/イーサネット - 最大125 MS/s - 16ビット - LXI(Gbitイーサネット)インターフェース搭載16ビット・デジタイザ - 125 MS/s、40 MS/s、20 MS/s、5 MS/sモデル - 48、40、32、24チャンネル・モデル - 最大60 MHzの帯域幅 - 入力レンジ:± 200 mV~± 10 V - 全チャンネル同時サンプリング - チャンネルごとにADCとアンプを分離 - 全機能のリモート・コントロール - 16種類のモデルを用意 ...

... デジタル・アクイジション/ロジック・アナライザ - PCIe 32チャンネル・デジタル波形収集 - 720 MBit/s 内部サンプリング・レート・タイミング - 700 MBit/s 外部状態クロック - 4 GByte (32 GBit)のオンボード・メモリを標準装備 - 差動インターフェース(LVDS)バージョンあり - シングルエンド(1.2V、1.5V、1.8V、2.5V、3.3V、5V)バージョンあり - FIFOモード連続ストリーミング - 最大8枚=256チャンネルの同期(Star-Hub使用時) - ...

... ソフトウェアで選択可能なアナログゲインによる4Vppの入力範囲 グラフィカルツールSCI-CompilerによるオープンFPGAプログラミング 幅広いアプリケーション(原子核・素粒子物理学から高タイミング分解能、高速中性子分光、国土安全保障まで) PMTまたはSiPMに結合された液体または無機シンチレータ、またはシリコンおよびHPGe検出器からの信号に適しています。 スコープモード(コモントリガ)とDPPモード(独立チャンネルセルフトリガ)をオンボードでライブ選択可能。 DPPアルゴリズムの幅広い選択(PHA、PSD、ZLE、DAWなど) マルチボード同期とシステム構築機能 フロント・パネルの完全プログラマブルI/O(LEMO ...

CAEN Spa

... - 128/32チャンネル、14ビット@125 MS/sデジタイザ - オープンFPGAとSci-Compilerソフトウェアによる容易なファームウェア開発 - ラックまたはデスクトップ・フォーム・ファクタ - R5560/R5560SE 128チャンネル(ディファレンシャルまたはシングルエンド)ラックマウントで大規模な実験に対応 特に中性子検出アプリケーションにおいて、大型検出器アレイの読み出しが可能 ...

CAEN Spa

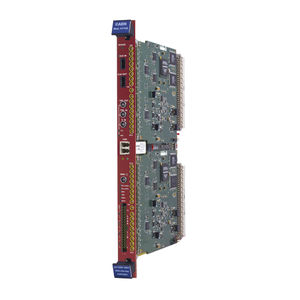

... CAEN Mod.V1742は、1ユニット幅のVME 6Uモジュールで、32+2チャネル12ビット5GS/sスイッチド・キャパシタ・デジタイザ・セクションを搭載しています。入力ダイナミックレンジは、シングルエンドのMCX同軸コネクタで1 Vppです(DCオフセットを制御するために各チャネルに16ビットDAC)。 デジタイザは、スイッチド・キャパシタ・アレイDRS4チップ(Domino Ring Sampler)をベースにしている。この技術は、1024個のコンデンサ(アナログ・メモリ)を並べたもので、アナログ入力信号が円形に連続的にサンプリングされる。 サンプリング周波数はデフォルトで5GHzで、2.5GHz、1GHz、750MHzにプログラムできる。アナログからデジタルへの変換は、チップのサンプリング・フェーズと同時ではなく、トリガ条件が満たされるとすぐに開始されるため、アナログ入力のみがデジタル化される場合は110μs、高速トリガTRnもデジタル化される場合は181μsのデッドタイムが発生する。トリガーが ...

CAEN Spa

... DT5740は、32チャネル12ビット62.5MS/s(外部クロック使用時65MS/s)デスクトップ波形デジタイザで、ERNI SMCコネクタの2Vppシングルエンド入力ダイナミクスを備えています。16チャンネルはMCX同軸コネクターでも使用可能です。10Vpp(シングルエンド)入力フルスケールレンジのバージョンもあります(DT5740C)。DCオフセットは、各8チャンネル・グループの16ビットDACを介して±1 V(±5 V)の範囲で調整可能です。 このモジュールは、フロントパネルのクロック入力と、内部/外部基準からのクロック合成用のPLLを備えています。データ・ストリームはサーキュラー・メモリ・バッファに連続的に書き込まれます。トリガーが発生すると、FPGAはポスト・トリガー用にさらにN個のサンプルを書き込み、USBまたは光リンクで読み込めるバッファをフリーズします。このバッファはUSBまたは光リンクで読み出すことができます。 各チャンネルには、192kSのSRAMマルチイベント・バッファがあり、プログラム可能なサイズの1÷1024バッファに分割できます。フリーズしたバッファの(USBまたは光リンクによる)読み出しは、アクティブなサーキュラー・バッファ(ADCデータ・ストレージ)への書き込み動作から独立しています。 DT5740はマルチボード同期をサポートしており、すべてのADCを共通のクロック源に同期させ、トリガのタイムスタンプを確実に合わせることができます。一度同期がとれれば、すべてのデータは複数のDT5740ボード間でアライメントされ、コヒーレントとなります。 トリガ信号は、フロント・パネルのトリガ入力やソフトウェア経由で外部から供給できますが、スレッショルド・セルフ・トリガ機能により内部で生成することもできます。 DT5740は、USB ...

CAEN Spa

改善のご提案 :

詳細をお書きください:

サ-ビス改善のご協力お願いします:

残り