Up to 5 GS/s digitizer V174232-channel12-bitPCIe

Add to favorites

Compare this product

Characteristics

- Speed

- up to 5 GS/s

- Number of channels

- 32-channel

- Options

- 12-bit, PCIe, VME

Description

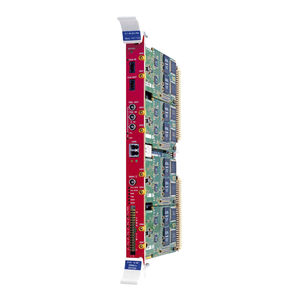

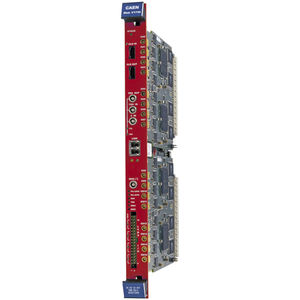

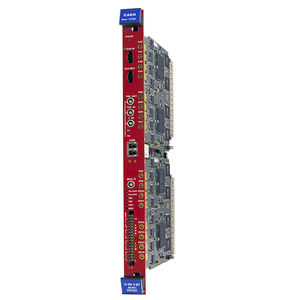

The CAEN Mod. V1742 is a 1-unit wide VME 6U module housing 32+2 Channel 12 bit 5 GS/s Switched Capacitor Digitizer sections. The input dynamic range is 1 Vpp on single-ended MCX coaxial connectors (16-bit DAC on each channel to control the DC Offset).

The digitizer is based on the Switched Capacitor Array DRS4 chip (Domino Ring Sampler). This technology relies on a series of 1024 capacitors (analog memory) in which the analog input signal is continuously sampled in a circular way.

The sampling frequency is 5 GHz by default and it can be programmed to 2.5 GHz, 1GHz, and 750 MHz. The analog to digital conversion is not simultaneous with the chip sampling phase, and it starts as soon as the trigger condition is met, thus producing a dead time of 110 μs in case only the analog inputs are digitized, 181 μs when also the fast trigger TRn is digitized. When the trigger stops the DRS4 chip sampling (holding phase), the analog memory buffer is frozen, and the cell content is made available to the 12 bit ADC for the digital conversion.

The digital memory allows to store subsequent events, even if the readout is not yet started. Moreover, since the digital memory buffers work like FIFOs, the readout activity from VME or Optical Link does not affect write operations of subsequent events.

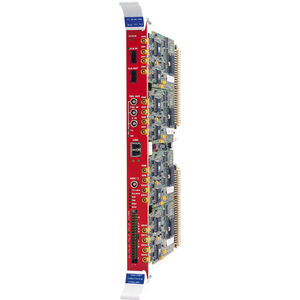

The available trigger sources are:

• External Trigger, trigger on TRG-IN connector, common to all enabled groups.

• Fast (Low Latency) Local Trigger, trigger on TR0 and TR1 connectors, common to couples of groups. This mode is called “Fast” or “Low Latency” since the trigger latency to hold the DRS4 is reduced with respect to the external trigger.

Catalogs

No catalogs are available for this product.

See all of CAEN Spa‘s catalogs*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.