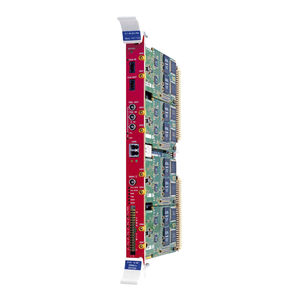

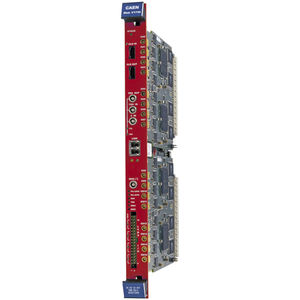

Up to 3.2 GS/s digitizer V174316-channelPCIeVME

Add to favorites

Compare this product

Characteristics

- Speed

- up to 3.2 GS/s

- Number of channels

- 16-channel

- Options

- PCIe, VME

Description

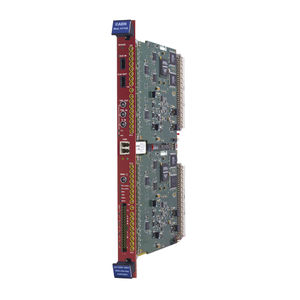

The CAEN Mod. V1743 is a VME 6U module housing 16 Channel 12 bit 3.2 GS/s Switched Capacitor Digitizer, with 2.5 Vpp single-ended input dynamics, issued from the collaboration with CEA/IRFU & CNRS/IN2P3/LAL and based on SAMLONG chip. A programmable DAC on each channel allows for DC Offset adjustment in the ±1.25 V range.

The analog input signals are continuously sampled into the SAMLONGs (sampling intervals down to 312.5 ps) in a circular analog memory buffer (1024 cells). As a trigger signal arrives, all analog memory buffers are frozen and subsequently digitized with a resolution of 12 bits into a digital memory buffer. During analog to digital conversion process, the V1743 cannot handle other triggers (Dead Time: 115 us).

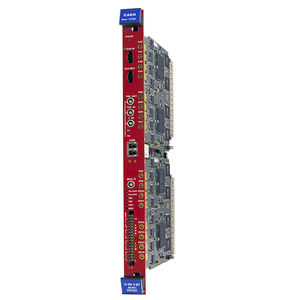

The memory buffer allows to store up to 7 full events for each cannel (1 event = 1024x12bit). The buffer can be read by VME bus or Optical Link simultaneously with write operation of successive events.

The module features front panel Clock Input and Output, as well as a PLL for clock synthesis from internal/external references. V1743 supports multi-board synchronization allowing all switched capacitor memories to be synchronized to a common clock source and ensuring Trigger time stamps alignment. Once synchronized, all data will be aligned and coherent across multiple V1743 boards

Catalogs

No catalogs are available for this product.

See all of CAEN Spa‘s catalogs*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.