- Robotics - Automation - Industrial IT

- Industrial Computing

- Dual core processor

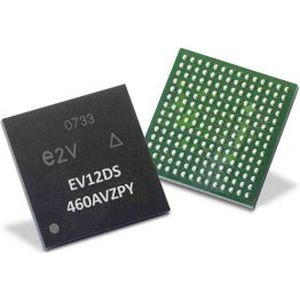

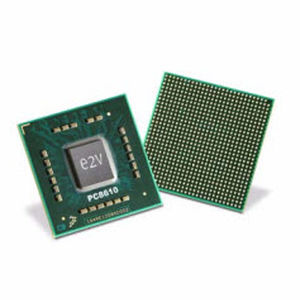

- e2v scientific instruments

Dual core processor PC8572E

Add to favorites

Compare this product

Characteristics

- Core number

- dual core

Description

FEATURES

• Dual Embedded e500 Cores, Scaling up to 1.5 GHz

– 6897 MIPS at 1500 MHz (Estimated Dhrystone 2.1)

• 36‐bit Physical Addressing

• Enhanced Hardware and Software Debug Support

• Double‐precision Floating Point Unit

• Memory Management Unit

• Integrated L1/L2 Cache

– L1 Cache: 32 KB Data and 32 KB Instruction Cache with

Line‐locking Support

– Shared L2 Cache: 1 MB with ECC

– L1 and L2 Hardware Coherency

– L2 Configurable as SRAM, Cache and I/O Transactions can

be Stashed Into L2 Cache Regions

• Integrated DDR Memory Controller with Full ECC Support,

Supporting:

– 333 MHz Clock Rate (667 MHz data rate), 64‐bit, 1.8V

SSTL, DDR2 SDRAM

– 400 MHz Clock Rate (up to 800 MHz Data Rate), 64‐bit,

1.5V SSTL, DDR3 SDRAM

• Application Acceleration Platform

– Advanced TLU

– Integrated Security Engine Supporting DES, 3DES, MD‐5,

SHA‐1/2, AES, RSA, RNG, Kasumi F8/F9 and ARC‐4

Encryption Algorithms

– Integrated PME (Regular Expression)

– Packet Deflate Engine

– Integrated Security Engine with XOR

• Four On‐chip, Triple‐speed Ethernet Controllers Supporting

10 and 100 Mbps, and 1 Gbps Ethernet/IEEE 802.3 Networks

with MII, RMII, GMII, SGMII, RGMII, RTBI and TBI Physical

Interfaces and IEEE 1588

– TCP/IP Checksum Acceleration and Advanced QoS

Features

– Lossless Flow Control

• General‐purpose I/O

• Serial RapidIO and PCI Express High‐speed Interconnect

Interfaces

• On‐chip Network (OCeaN) Switch Fabric

• 133 MHz, 32‐bit, 3.3V I/O, Local Bus with Memory

Controller

• Dual Integrated DMA Controller

• Dual I

2

C and DUARTS

• Programmable interrupt Controller

• IEEE 1149.1 JTAG Test Access Port

• 1.1V Core Voltage with 3.3V/2.5V/1.8V I/O

• 1023‐pin PBGA Package

Catalogs

No catalogs are available for this product.

See all of e2v scientific instruments‘s catalogs*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.