- Robotics - Automation - Industrial IT

- Industrial Computing

- Processor

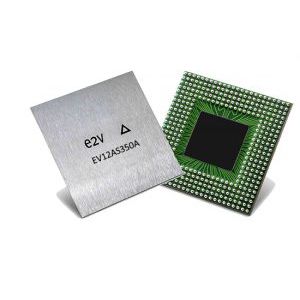

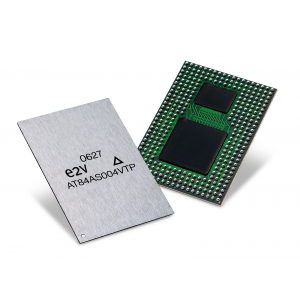

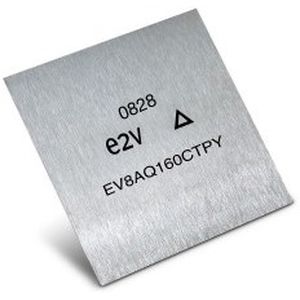

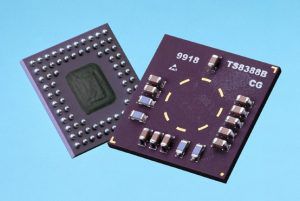

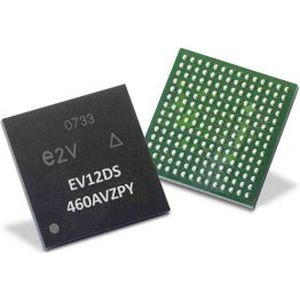

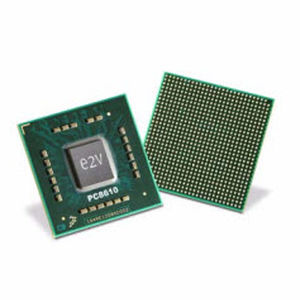

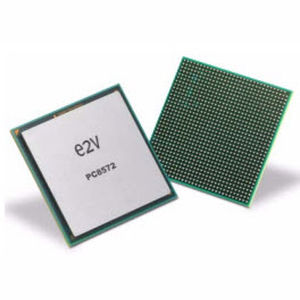

- e2v scientific instruments

Processor PC8540

Add to favorites

Compare this product

Description

Features

• Embedded e500 Book E-compatible Core Available up to 833 MHz

– 32-bit, Dual-issue, Superscalar, Seven-stage Pipeline

– 1850 MIPS at 800 MHz (Est. Dhrystone 2.1)

– 32 KB L1 Data and 32 KB L1 Instruction Cache with Line Locking Support

– 256 KB On-chip L2 Cache with Direct Mapped Capability

– Enhanced Hardware and Software Debug Support

– Memory Management Unit (MMU)

– SIMD Extension with Single Precision Floating Point

• Two TSECs Supporting 10/100/1000 Mbps Ethernet (IEEE® 802.3, 802.3u, 802.3x,

802.3z, and 802.3 ac-compliant) with Two GMII/TBI/RGMII Interfaces

• 166 MHz, 64-bit, 2.5V I/O, DDR SDRAM Memory Controller with Full ECC Support

• 500 MHz, 8-bit, LVDS I/O, RapidIO Controller

• 133 MHz, 64-bit, 3.3V I/O, PCI-X 1.0a/PCI 2.2 Bus Controller

• 166 MHz, 32-bit, 3.3V I/O, Local Bus with Memory Controller

• Integrated Four-channel DMA Controller

• Interrupt Controller

• IEEE 1149.1 JTAG Test Access Port

• 1.2V Core Voltage with 3.3V and 2.5V I/O

Description

The PC8540 contains a PowerPC® processor core. The PC8540 integrates a processor that implements the PowerPC

architecture with system logic required for networking, storage, and general-purpose embedded applications. For functional

characteristics of the processor, refer to the PC8540 Integrated Processor Preliminary Reference Manual.

Catalogs

No catalogs are available for this product.

See all of e2v scientific instruments‘s catalogs*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.