- Electricity - Electronics

- Electronic Component

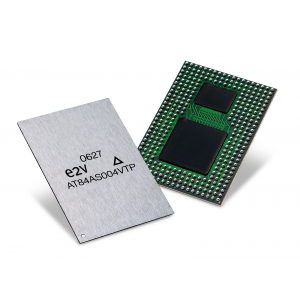

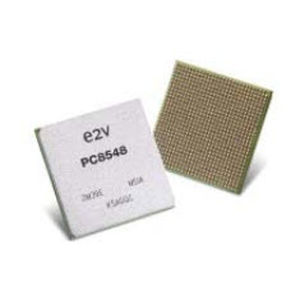

- 32-bit microcontroller

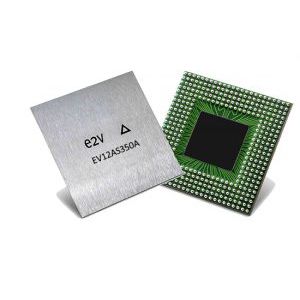

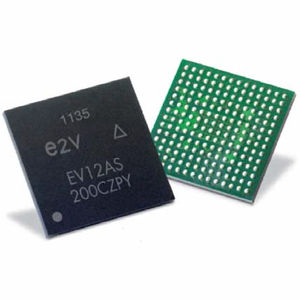

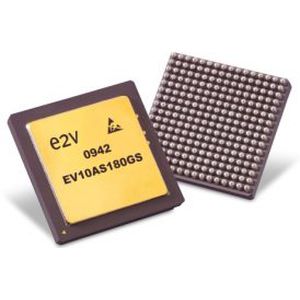

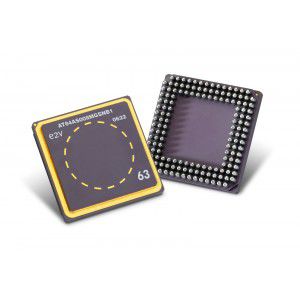

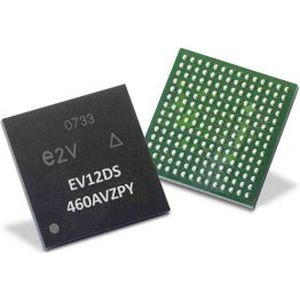

- e2v scientific instruments

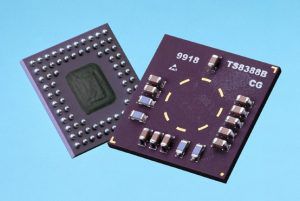

32-bit microcontroller TS68EN360

Add to favorites

Compare this product

Characteristics

- Type

- 32-bit

Description

Features

• CPU32+ Processor (4.5 MIPS at 25 MHz)

– 32-bit Version of the CPU32 Core (Fully Compatible with the CPU32)

– Background Debug Mode

– Byte-misaligned Addressing

• Up to 32-bit Data Bus (Dynamic Bus Sizing for 8 and 16 Bits)

• Up to 32 Address Lines (At Least 28 Always Available)

• Complete Static Design (0 - 25 MHz Operation)

• Slave Mode to Disable CPU32+ (Allows Use with External Processors)

– Multiple QUICCs Can Share One System Bus (One Master)

– TS68040 Companion Mode Allows QUICC to be a TS68040 Companion Chip and Intelligent Peripheral

(22 MIPS at 25 MHz)

– Peripheral Device of TSPC603e (see DC415/D note)

• Four General-purpose Timers

– Superset of MC68302 Timers

– Four 16-bit Timers or Two 32-bit Timers

– Gate Mode Can Enable/Disable Counting

• Two Independent DMAs (IDMAs)

• System Integration Module (SIM60)

• Communications Processor Module (CPM)

• Four Baud Rate Generators

• Four SCCs (Ethernet/IEEE 802.3 Optional on SCC1-Full 10 Mbps Support)

• Two SMC

• VCC = +5V ± 5%

• fmax = 25 MHz and 33 MHz

• Military Temperature Range: -55°C < TC < +125°C

• PD = 1.4W at 25 MHz; 5.25V

2W at 33 MHz; 5.25V

Description

The TS68EN360 QUad Integrated Communication Controller (QUICC™) is a versatile one-chip integrated microprocessor

and peripheral combination that can be used in a variety of controller applications. It particularly excels in communications

activities. The QUICC (pronounced “quick”) can be described as a next-generation TS68302 with higher performance in all

areas of device operation, increased flexibility, major extensions in capability, and higher integration.

Catalogs

No catalogs are available for this product.

See all of e2v scientific instruments‘s catalogsRelated Searches

- Signal amplifying integrated circuit

- Transceiver module

- RF transceiver

- Low-noise amplifying integrated circuit

- Microcontroller

- CMOS image sensor

- Infrared imaging sensor

- Programmable IC converter

- ADC IC converter

- Low-power transceiver module

- High-speed IC converter

- Visible image sensor

- 32-bit microcontroller

- High-speed image sensor

- DAC IC converter

- Multi-channel IC converter

- Isolation amplifying integrated circuit

- High-sensitivity image sensor

- Near-infrared image sensor

- In-line amplifier

*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.