Design software Oasys-RTL™qualityanalysiscreation

Add to favorites

Compare this product

Characteristics

- Function

- analysis, quality, design, creation, optimization, editing, synthesis

- Applications

- flow, RTLS

Description

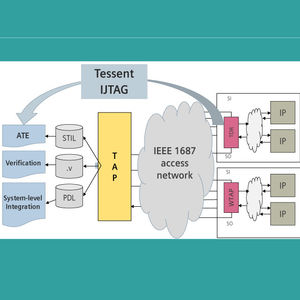

Oasys-RTL addresses the need for higher capacity, faster runtimes, improved QoR, and physical awareness by optimizing at a higher level of abstraction and using integrated floorplanning and placement capabilities.

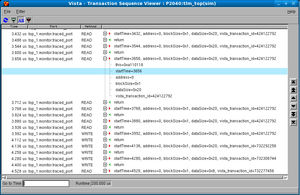

Fast, High-Quality Physical RTL Synthesis

Oasys-RTL provides better quality of results by enabling physical accuracy, floorplanning, and fast optimization iterations to get to design closure on time.

Power-Aware Synthesis

The power-aware synthesis capabilities include support for multi-threshold libraries, automatic clock gating, and UPF based Multi-VDD flow. During synthesis Oasys-RTL inserts all the appropriate level shifters, isolation cells and retention registers depending on the power intent as defined in the UPF.

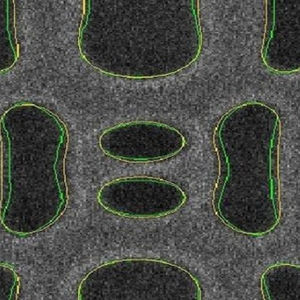

Create a Floorplan Directly From RTL

Oasys-RTL can create a floorplan directly from the design RTL using design dataflow and timing, power, area, and congestion constraints. It considers regions, fences, blockages and other physical guidance using the advanced floorplan editing tools and automatically places macros, pins, and pads.

Unique Placement-First Method

Rather than synthesizing first, then trying to optimize the gates, Oasys-RTL concurrently optimizes higher-level RTL partitions where it has a greater ability to converge on the best solution.

Catalogs

No catalogs are available for this product.

See all of SIEMENS EDA‘s catalogsRelated Searches

- Automation software solution

- Management software solution

- Analysis software solution

- Process software solution

- Computer-aided design software

- Windows software solution

- Control software solution

- Online software

- Real-time software solution

- Design software solution

- 3D software solution

- Interface software

- Measurement software

- Industrial software solution

- Quality software

- Simulation software

- Visualization software solution

- Automated software

- Development software

- Network software solution

*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.