Design software Aprisadatabasequalityanalysis

Add to favorites

Compare this product

Characteristics

- Function

- analysis, quality, design, database, optimization

- Applications

- process, architecture

Description

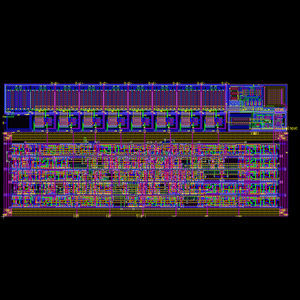

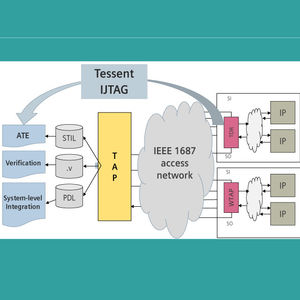

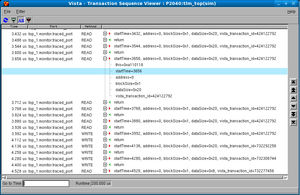

Designing at advanced process nodes requires a new place-and-route paradigm to manage the increasing complexity. Aprisa is a detail-route-centric physical design platform for the modern SoC.

Accelerate SoC design with place-and-route technology

Aprisa digital implementation is an RTL2GDSII solution that offers complete synthesis and place-and-route functionality for top-level hierarchical designs and block-level implementation. It's tapeout quality correlation with signoff tools, both for STA timing and DRC, reduces design closure and ensures optimal performance, power and area (PPA).

Benefits of using Aprisa SoC design software?

Aprisa delivers optimal PPA out-of-the-box. This helps physical designers reduce the effort at each step of the place-and-route flow and achieve faster time-to-market

Fast design closure

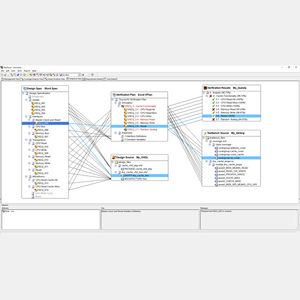

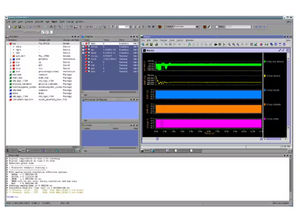

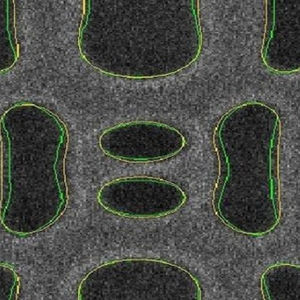

Unified architecture and common analysis engines ensure excellent timing and DRC correlation between implementation steps and with signoff tools, greatly reducing the number of flow iterations and ECOs

AI technologies to aid designers on tasks

AI-driven Auto Macro Placement (AMP) technology delivers expert designer quality macro placement at a fraction of the time

Unmatched out-of-the-box PPA

Aprisa's detail-route-centric architecture delivers excellent out-of-the-box results through reference flows that eliminate the need for place groups or margins during placement and CTS

Best cost-of-ownership

Certified at the most advanced nodes by the main Foundries,

while supporting mature nodes. Aprisa is the easiest digital implementation solution to adopt and the most efficient for both engineering and computing resources

VIDEO

Catalogs

No catalogs are available for this product.

See all of SIEMENS EDA‘s catalogsRelated Searches

- Automation software solution

- Management software solution

- Analysis software solution

- Process software solution

- Windows software solution

- Computer-aided design software

- Control software solution

- Real-time software solution

- Online software

- Design software solution

- 3D software solution

- Measurement software

- Interface software

- Industrial software solution

- Quality software

- Simulation software

- Visualization software solution

- Automated software

- Development software

- Network software solution

*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.