Visualization software Xpedition Substrate Integratordesignmanagementprototyping

Add to favorites

Compare this product

Characteristics

- Function

- management, visualization, design, planning, optimization, verification, connectivity, prototyping

- Applications

- process

- Type

- 3D

Description

Heterogeneous and homogeneous 2.5/3D IC Package Connectivity Planning, assembly prototyping, & system technology co-optimization.

2.5/3D IC Package Planning & Prototyping

Early prototyping and exploration allows engineers to evaluate different ASIC/chiplet, interposer, package, and PCB integration scenarios in order to meet overall PPA, device size, routability, and cost goals prior to detailed physical implementation.

Key features of Substrate Integrator

Full or Partial Schematics Import

IC package assembly logical connectivity can be constructed by using full or partial graphical schematics, useful for high device count designs such as SiP modules and/or the re-use/retargeting of previous designs.

System-level Package Connectivity Management

System connectivity management, visualization, and system-level logical verification of multi-die, multi-component, and multi-substrate IC package designs.

Aggregation of Die, Chiplets & Substrates

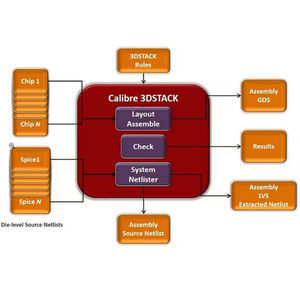

Xpedition Substrate Integrator integrates die, chiplets, and interposers from different process nodes and suppliers. Multiple formats are supported including LEF/DEF, GDS, AIF, and CSV/TXT. Hierarchical virtual die models support bidirectional ECO changes of objects under design/optimization.

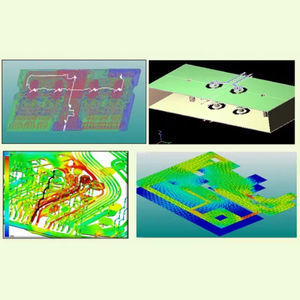

Silicon-package-PCB Cross Substrate Co-optimization

Cross-substrate planning and co-optimization greatly improve predictability during implementation by finding and fixing issues before they become late-stage surprises. A system perspective with cross-substrate visibility improves communication and coordination through immediate feedback to decisions typically made on an individual substrate basis.

Catalogs

Related Searches

- Automation software solution

- Management software solution

- Analysis software solution

- Process software solution

- Windows software solution

- Computer-aided design software

- Control software solution

- Real-time software solution

- Online software

- Design software solution

- 3D software solution

- Measurement software

- Interface software

- Industrial software solution

- Quality software

- Simulation software

- Visualization software solution

- Automated software

- Development software

- Network software solution

*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.