Design software Simulink Design Verifier™diagnosticverification

Add to favorites

Compare this product

Characteristics

- Function

- design, diagnostic, verification

Description

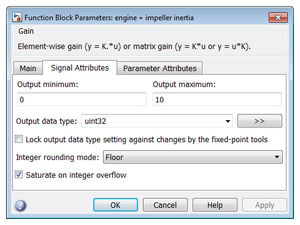

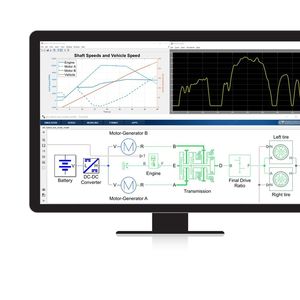

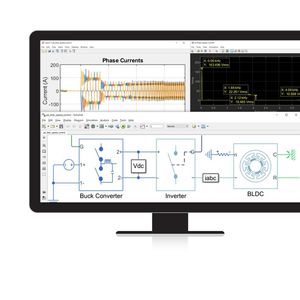

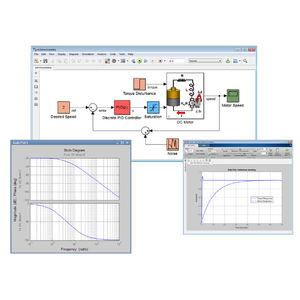

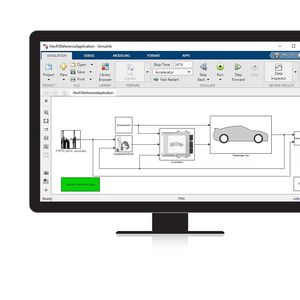

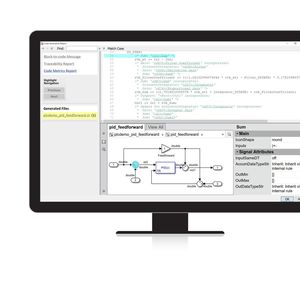

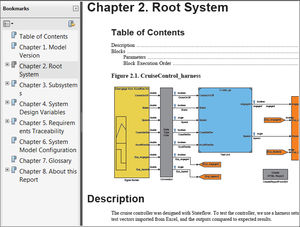

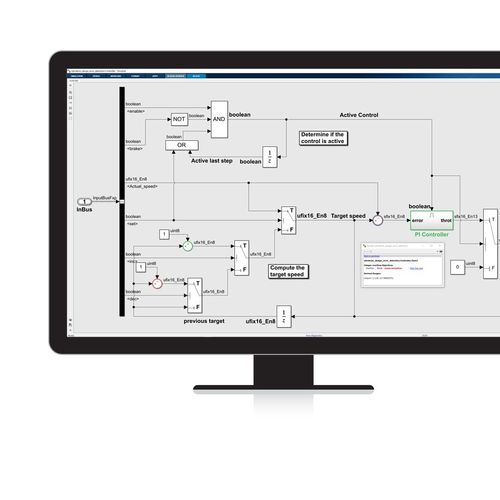

Simulink Design Verifier™ uses formal methods to identify hidden design errors in models. It detects blocks in the model that result in integer overflow, dead logic, array access violations, and division by zero. It can formally verify that the design meets functional requirements. For each design error or requirements violation, it generates a simulation test case for debugging.

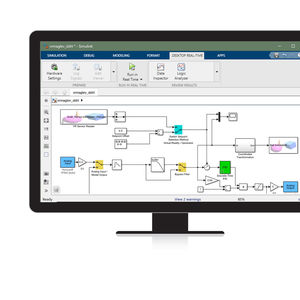

Simulink Design Verifier generates test cases for model coverage and custom objectives to extend existing requirements-based test cases. These test cases drive your model to satisfy condition, decision, modified condition/decision (MCDC), and custom coverage objectives. In addition to coverage objectives, you can specify custom test objectives to automatically generate requirements-based test cases.

Support for industry standards is available through IEC Certification Kit (for ISO 26262 and IEC 61508) and DO Qualification Kit (for DO-178 and DO-254).

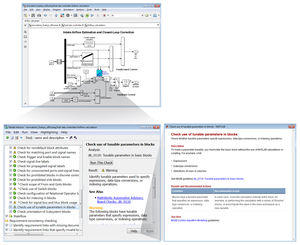

Design Error Detection

Discover design errors in your model before simulation, including run-time errors, diagnostic errors, and dead logic.

VIDEO

Catalogs

Related Searches

- Automation software solution

- Management software solution

- Analysis software solution

- Process software solution

- Windows software solution

- Computer-aided design software

- Control software solution

- Real-time software solution

- Online software

- Design software solution

- 3D software solution

- Measurement software

- Simulation software

- Visualization software solution

- Programming software

- Automated software

- Network software solution

- Machine software

- Engineering software

- Test software

*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.