- Electricity - Electronics

- Electronic Component

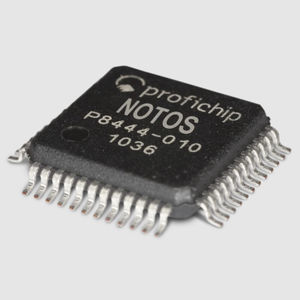

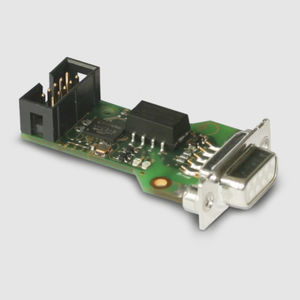

- Digital microchip

- YASKAWA Europe GmbH

Digital microchip SNAP+analogdetection

Add to favorites

Compare this product

Characteristics

- Options

- analog, digital, detection

Description

Basic SliceBus backplane information:

Single master system

Up to 64 slave (Node) stations

Asynchronous, serial data transmission with 48 MBit/s over Point to Point LVDS physic

Additional alarm line for initialization and asynchronous event communications from node to master

Full system detection from SliceBus master without external information on module configuration

Error detection mechanism:

CRC code with Hamming distance 4 for every telegram (all 3 bit errors will be detected)

Watchdog function inside every node for SliceBus master observation

"Auto shut down" in case of SliceBus master malfunction

Retry statistic for early detection of possible transmission issues

Time-synchronisation:

Every node has its own clock with 1 µs resolution

All node clocks are synchronized with the SliceBus master (accuracy <100ns)

Option for clock synchronization from SliceBus master to SliceBus master via different protocols

(Profibus DP V2, Profinet, Ethercat,...)

SNAP+ Technological functions:

Standard I/O function: 8 digital I/O or up to 32 I/O with shift register

Integrated digital input filter function

Asynchronous event signaling with µs time stamping for advanced nodes

Two advanced counters with AB oversampling, latch, reset, output, hysteresis, comparevalue, repetitive/endless counting and additional time stamp information

SSI function with time stamp information (speed calculations: counter difference/time)

Pulse Width Modulation with 20 ns resolution

Frequency measurement mode

Special digital I/O time stamp nodes (ETS: Edge Time Stamp System) for input edge and output control with 1 µs resolution (independent from fieldbus cycle!)

Catalogs

No catalogs are available for this product.

See all of YASKAWA Europe GmbH‘s catalogs*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.