- Robótica - Automação - Informática

- Informática industrial

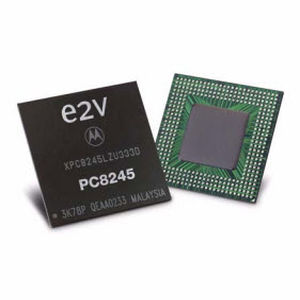

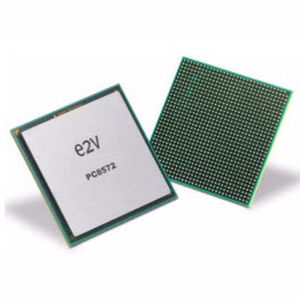

- Microprocessador com 2 núcleos

- e2v scientific instruments

Microprocessador com 2 núcleos PC8572E

Guardar nos favoritos

Comparar

Características

- Número de núcleos

- com 2 núcleos

Descrição

CARACTERÍSTICAS

- Dual Embedded e500 Cores e500, escalando até 1,5 GHz

- 6897 MIPS a 1500 MHz (estimativa de Dhrystone 2.1)

- Endereçamento Físico de 36 bits

- Suporte aprimorado de Depuração de Hardware e Software

- Unidade de duplo ponto flutuante de precisão

- Unidade de gestão de memória

- Cache L1/L2 integrado

- Cache L1: 32 KB Dados e 32 KB Instrução Cache com

Suporte de bloqueio de linha

- Cache L2 partilhado: 1 MB com CEC

- Coerência de Hardware L1 e L2

- L2 Configurável como SRAM, cache e transações de E/S podem

estar escondido nas regiões de cache L2

- Controlador de memória DDR integrado com suporte total de ECC,

Apoio:

- Taxa de relógio de 333 MHz (taxa de dados de 667 MHz), 64 bits, 1.8V

SSTL, DDR2 SDRAM

- Taxa de relógio de 400 MHz (taxa de dados de até 800 MHz), 64 bits,

1.5V SSTL, DDR3 SDRAM

- Plataforma de aceleração de aplicações

- TLU Avançado

- Motor de Segurança Integrado de Suporte DES, 3DES, MD-5,

SHA-1/2, AES, RSA, RNG, Kasumi F8/F9 e ARC-4

Algoritmos de criptografia

- PME Integrado (Expressão Regular)

- Motor de esvaziamento de pacotes

- Motor de Segurança Integrado com XOR

- Quatro controladores Ethernet de velocidade tripla suportados por quatro controladores On-chip

10 e 100 Mbps, e 1 Gbps Ethernet/IEEE 802.3 Networks

com MII, RMII, GMII, SGMII, RGMII, RTBI e TBI Físico

Interfaces e IEEE 1588

- Aceleração do checksum TCP/IP e QoS avançado

Funcionalidades

- Controle de fluxo sem perda

- E/S de uso geral

- Interconexão serial RapidIO e PCI Express de alta velocidade

Interfaces

- Rede On-chip (OCeaN) Switch Fabric

- 133 MHz, 32-bit, 3.3V I/O, barramento local com memória

Controlador

- Controlador DMA integrado duplo

- Dual I

2

C e DUARTS

- Controlador de interrupção programável

- IEEE 1149.1 Porta de Acesso ao Teste JTAG

- Tensão de núcleo de 1,1V com 3,3V/2,5V/1,8V I/O

- Pacote PBGA de 1023 pinos

---

Catálogos

Não estão disponíveis catálogos para este produto.

Ver todos os catálogos da e2v scientific instrumentsOutros produtos e2v scientific instruments

Semiconductors

* Os preços não incluem impostos, transporte, taxas alfandegárias, nem custos adicionais associados às opções de instalação e de ativação do serviço. Os preços são meramente indicativos e podem variar em função dos países, do custo das matérias-primas e das taxas de câmbio.