- Eletricidade - Eletrônica

- Componente Eletrônico

- Microcontrolador 32 bits

- e2v scientific instruments

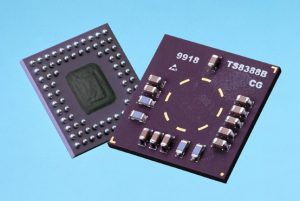

Microcontrolador 32 bits TS68EN360

Guardar nos favoritos

Comparar

Características

- Tipo

- 32 bits

Descrição

Características

• Processador de CPU32+ (4,5 MIPS em 25 megahertz)

– versão de 32 bits do núcleo CPU32 (inteiramente - compatível com o CPU32)

– O fundo elimina erros do modo

– endereçamento Byte-desalihnado

• Até ônibus de dados de 32 bits (cola dinâmica do ônibus para 8 e 16 bocados)

• Até 32 linhas do endereço (pelo menos 28 sempre disponíveis)

• Projeto estático completo (uma operação de 0 - 25 megahertz)

• Escravo Mode para desabilitar CPU32+ (permite o uso com processadores externos)

– QUICCs múltiplo pode compartilhar de um ônibus de sistema (um mestre)

– O modo do companheiro TS68040 permite que QUICC seja uma microplaqueta do companheiro TS68040 e um periférico inteligente

(22 MIPS em 25 megahertz)

– Dispositivo periférico de TSPC603e (veja a nota de DC415/D)

• Quatro temporizadores de uso geral

– Superset dos temporizadores MC68302

– Quatro temporizadores de 16 bits ou dois temporizadores de 32 bits

– O modo da porta pode permitir/desabilitar a contagem

• Dois DMAs independente (IDMAs)

• Módulo da integração de sistemas (SIM60)

• Módulo de processador das comunicações (CPM)

• Quatro Baud Rate Generators

• Quatro SCCs (Ethernet/IEEE 802,3 opcional no apoio de SCC1-Full 10 Mbps)

• Dois SMC

• VCC = ± 5% de +5V

• fmax = 25 megahertz e 33 megahertz

• Variação da temperatura militar: -55°C < TC < +125°C

• Paládio = 1.4W em 25 megahertz; 5.25V

2W em 33 megahertz; 5.25V

Descrição

O controlador de comunicação TS68EN360 integrado quadrilátero (QUICC™) é um-microplaqueta versátil um microprocessador integrado

e combinação periférica que pode ser usada em uma variedade de aplicações do controlador. Prima particularmente nas comunicações

atividades. O QUICC (pronunciado “rápido ") pode ser descrito como uma próxima geração TS68302 com desempenho mais alto em tudo

áreas da operação do dispositivo, da flexibilidade aumentada, de extensões principais na capacidade, e da integração mais alta.

---

Catálogos

Não estão disponíveis catálogos para este produto.

Ver todos os catálogos da e2v scientific instrumentsOutros produtos e2v scientific instruments

Semiconductors

Pesquisas relacionadas

- Amplificador de sinal

- Transceptor

- Transceptor RF

- Amplificador de baixo ruído

- Microcontrolador

- Sensor de imagem CMOS

- Amplificador RF

- Circuito integrado conversor programável

- Sensor de imagem de infravermelho

- Conversor analógico / digital

- Transceptor de baixa potência

- Conversor alta velocidade

- Sensor de imagem visível

- Microcontrolador 32 bits

- Sensor de imagem de alta velocidade

- Circuito integrado conversor DAC

- Circuito integrado conversor multivias

- Amplificador de isolamento

- Sensor de imagem de alta sensibilidade

- Sensor de imagem NIR

* Os preços não incluem impostos, transporte, taxas alfandegárias, nem custos adicionais associados às opções de instalação e de ativação do serviço. Os preços são meramente indicativos e podem variar em função dos países, do custo das matérias-primas e das taxas de câmbio.