- Produtos

- Placa FPGA

- UEI - United Electronic Industries

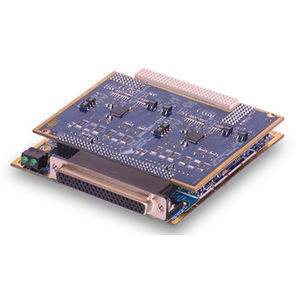

Placa FPGA DNx-PL-820 series

Guardar nos favoritos

Comparar

Descrição

Os DNx-PL-820 são placas FPGA programáveis pelo utilizador. A placa permite a um programador FPGA adicionar funcionalidades FPGA personalizadas à família DNx e às várias plataformas que a suportam.

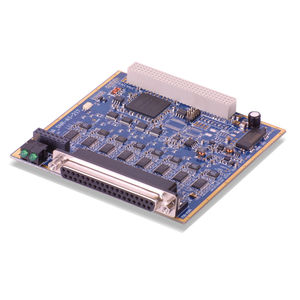

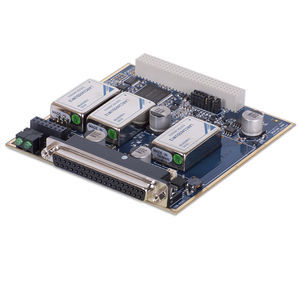

O DNx-PL-820 é um produto de duas placas, de base/filha. A prancha inferior (esquerda num DNR RACK) inclui um Cyclone II FPGA enquanto a prancha superior (direita no RACK) fornece um MAX 10 FPGA. A placa TheCyclone é utilizada exclusivamente como interface entre o DNxbus e o chip MAX 10 FPGA. O chip MAX 10 é totalmente programável pelo utilizador utilizando as populares ferramentas de desenvolvimento Altera, incluindo o processador Nios II incorporado.

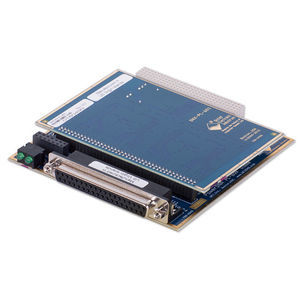

A placa MAX 10 permite que as aplicações FPGA desenvolvidas pelo utilizador sejam instaladas e executadas na placa. 104 pinos GPIO são retirados da placa MAX 10 FPGA e estão disponíveis para ligações à E/S do utilizador. 51bits são fornecidos no conector de E/S da placa Cyclone enquanto 53 são fornecidos no conector da placa MAX 10.

O MAX 10 tem uma variedade de características únicas e poderosas que fazem dele uma escolha ideal como um alvo FPGA personalizado. Incluído nestas características está uma capacidade única e instantânea que permite que a aplicação MAX 10 comece a funcionar imediatamente, sem considerar se o Cubeor RACKtangle completou o seu processo de boot-up. O MAX 10 também suporta o utilizador e a dupla configuração FLASH, blocos DSP e a funcionalidade de processador Nios IIembedded.

O chip MAX 10 pode ser programado por um interface JTAG que é trazido para o conector I/O ou pelo backplane de ADN (viathe Cyclone chip) por um utilitário fornecido pela UEI. Um conjunto de jumpers na placa permite que o interface JTAG seja desactivado quando os securityconcerns o mandam.

---

Catálogos

Não estão disponíveis catálogos para este produto.

Ver todos os catálogos da UEI - United Electronic IndustriesOutros produtos UEI - United Electronic Industries

I/O Interfaces

* Os preços não incluem impostos, transporte, taxas alfandegárias, nem custos adicionais associados às opções de instalação e de ativação do serviço. Os preços são meramente indicativos e podem variar em função dos países, do custo das matérias-primas e das taxas de câmbio.